# JMB362 PCI Express to SATA II Host Controller

### **Overview**

JMB362 is a single chip, 1-lane PCI Express to 2-port Serial ATA II Host Controller. JMB362 supports both AHCI and Legacy IDE controller to increase system feasibility, including Native Command Queuing, ATAPI Device, Port Multiplier with Command-based Switching, Hot Plugging like USB and eSATA (External SATA) connection on SATA port to enhance SATA II capability. It features PCI Express bus and Serial ATA II interface to express high performance storage devices.

JMB362 supports PCI Express to make trace length can be up to 8" (20.3cm). Although the maximum length is up to 8 inch, the trace length is as short as possible on real application.

JMB362 supports SATA II Gen1m and Gen2m for eSATA application through Programmable Output Swing Control and Receiver Sensitivity Control. From hardware design view, eSATA trace can be up to 15" (38.1cm) with proper layout style and some examples are list in following section. Although the maximum length is up to 15 inch, the trace length is as short as possible on real application. Of course, eSATA HDD connected with 2m eSATA cable must be supported according to SATA-IO definition.

#### **Feature**

#### Compliance

- Compliant with Serial ATA AHCI (Advanced Host Controller Interface) Spec. Reversion 1.0

- Compliant with Bus Master Programming interface for IDE ATA Controllers Revision 1.0

- Compliant with *PCI Express Base Spec. Revision 1.0a*

- Compliant with Serial ATA High Speed Serialized AT Attachment Spec. Revision 1.0a

- Compliant with Serial ATA II: Extensions to Serial ATA 1.0a Revision 1.1

- Compliant with Gen1i, Gen1m, Gen2i and Gen2m Serial ATA II: Electrical Spec. Revision 1.0

#### **Overall**

- Integrated 1-Lane PCI Express PHY and 2-port SATA II PHY

- Integrated two PLL for both PCI Express bus and SATA II interface

- Output swing control and Automatic impedance calibration for both PCI Express and SATA II PHY

- Supports a slave SMBus interface (follow System Management Bus Specification Revision 1.1)

- Fabricated 0.18um/3.3V UMC CMOS Standard Logic Process with 1.8V and 3.3V

- Available in 48-pin QFN package

- Pin compatible with JMB360 (1-port SATA II Host Controller)

#### **PCI Express**

- Supports 1-Lane 2.5Gbps PCI Express bus

- Internal native interface multiplexed to 2-port SATA II and 1-port PATA

- All registers accessible in unified memory space

- PCI Express PCB trace length can be up to 8" (20.3cm)

#### **SATA II**

- Supports 2-port 3.0Gbps SATA II interface

- Supports two independent SATA II channels (separate logic and FIFO)

- Supports Native Command Queue (NCQ) on SATA II port

- Supports Hot Plugging like USB on SATA II port

- Supports SATA II Gen1m and Gen2m (External SATA Connection, eSATA)

- Supports Port Multiplier with Command-based Switching on SATA II port

- SATA II PCB trace length can be up to 15" (38.1cm)

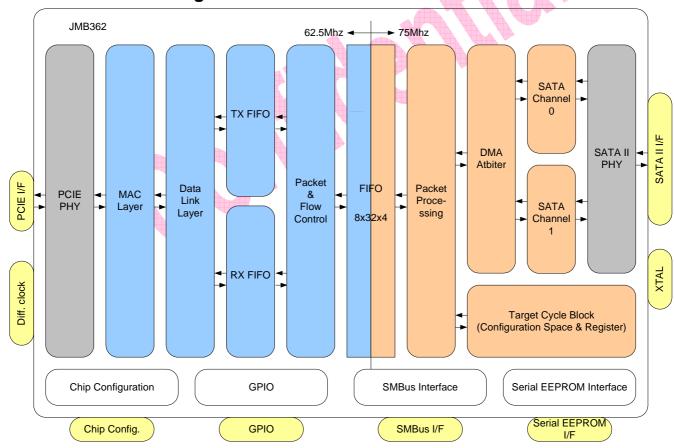

## **Functional Block Diagram**

**Functional Block Diagram of JMB362**

# **Product Information**

| Name   | Description                            |  |

|--------|----------------------------------------|--|

| JMB362 | PCI Express to SATA II Host Controller |  |

## **Document**

| 1 | JMB362 Data Sheet            |

|---|------------------------------|

| 2 | JMB362 Design Specification  |

| 3 | JMB362 Hardware Design Guide |

| 4 | JMB362 Hardware Schematic    |

# **Contact Information**

| Department    | Email             |

|---------------|-------------------|

| Sales         | sales@jmicron.com |

| Tech. Support | fae@jmicron.com   |